Testovací modul DDS

Ivo Dufek, UREL, FEEC, VUT Brno

xdufek06 feec.vutbr.cz

feec.vutbr.cz

Obsah:

- Úvod

- Realizace

- Závěr

- Literatura

Tento projekt řeší návrh hardware jednoduchého generátoru sinusového signálu s DDS typu AD9832 od firmy Analog Devices [1].

Jedná se o generátor na principu přímé číslicové syntézy s frekvenčním rozsahem 0 - 6MHz. Přípravek se vyznačuje nízkým proudovým odběrem a velmi

malými rozměry. Využití najde buď jako VFO jednoduchého přijímače (vysílače) KV, zdroj signálu pro rozmítač (wobbler) nebo jednoduše jako digitální

signální generátor.

Srdcem celého zařízení je obvod AD9832, jedná se o integrovaný obvod CMOS, sdružující v sobě kompletní jednotku DDS (Direct Digital Synthesis). Princip funkce tohoto obvodu je

následující (převzato z [2]):

Časový průběh sinusového signálu lze vyjádřit jako f(t) = sin(φ(t)), rozvineme člen φ(t) (okamžitou fázi signálu) jako součet j(t) = ω(t)t + φ0(t).

Pro konstantní kmitočet f(t) musí platit, že fáze φ(t) lineárně roste, tedy že ω(t) je v čase konstantní nebo že fáze φ0(t) se lineárně zvětšuje.

Jelikož ω(t) se zde neuplatňuje, zaměříme se na změnu fáze φ0. Lineárního zvětšování lze dosáhnout například pravidelným přičítáním stejného čísla Δφ s kmitočtem fclk.

Uvažujeme-li číslicový systém se stabilním hodinovým kmitočtem, můžeme označit po sobě jdoucí hodnoty fáze čísly N - 1, N, N + 1 a tak dále, takže hodnotu fáze φn+1 lze vypočíst jako φN+1 = φN + Δφ0.

Vyjádříme-li v číslicovém systému fázi n-bitovým číslem, pak může nabývat 2n hodnot a její změna se děje rychlostí Δφ0 = fclk * Δφ / 2N. Tento výraz je ekvivalentní ω a pro dané Δφ je konstantní.

Dále je patrné, že nejmenší rozlišitelný kmitočet je daný hodinovým kmitočtem a bitovou šířkou fáze s jejímž zvětšováním roste exponenciálně.

Obvod, provádějící přímou číslicovou syntézu, se skládá z registru změny fáze (Δ), akumulátoru fáze (Σ), funkční tabulky ROM, DAC, antialiasing filtru F a generátoru hodinového kmitočtu G.

Registr změny fáze Δ drží nastavenou hodnotu Δφ. Akumulátor fáze Σ při každém hodinovém pulzu fclk přičte Δφ k hodnotě fáze φ1 a její novou hodnotu si podrží až do příchodu dalšího hodinového pulzu.

Aby nemusela být ROM tabulka příliš veliká (a ani to není účelné z hlediska výstupního šumu), přivádí se do ní jen asi 12 až 14 horních bitů fáze (φ2).

V ROM tabulce jsou uloženy ve dvojkovém formátu hodnoty funkce sinus (nebo jiné, umožňuje-li obvod přepnutí tabulky nebo nahrání nového obsahu do RAM paměti) a její výstup je synchronně s hodinovým signálem přiveden do D/A převodníku, ve kterém již vzniká analogový sinusový signál.

Z principu činnosti D/A převodníku i skokových změn fáze však tento signál obsahuje i své harmonické složky, které se objevují nad polovinou hodinové frekvence a které zkreslují výstupní signál.

Proto je za D/A převodníkem ještě zařazen strmý filtr typu DP, který nežádoucí kmitočtové složky potlačí.

Maximální generovaný kmitočet fout = 6 MHz

Maximální proudový odběr je I = 24 mA při Ucc = 5 V

Rozsah napájecího napětí Ucc = 2,7–5 V

Rozlišení interního DA převodníku je 10 bitů

Frekvence hodin 25 MHz

Sériové ovládání po sběrnici SPI

Maximální generovaný kmitočet fout = 6 MHz

Maximální proudový odběr je I = 24 mA při Ucc = 5 V

Rozsah napájecího napětí Ucc = 2,7–5 V

Rozlišení interního DA převodníku je 10 bitů

Frekvence hodin 25 MHz

Sériové ovládání po sběrnici SPI

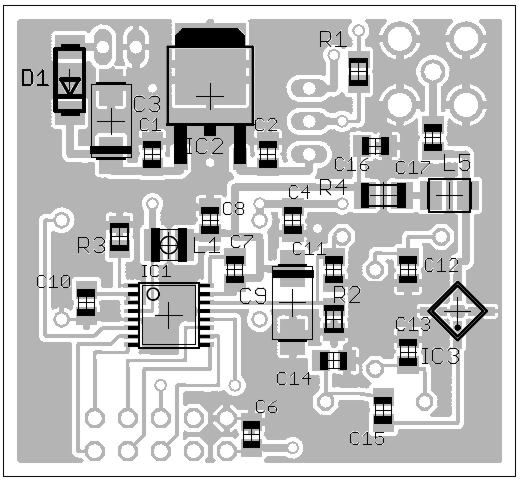

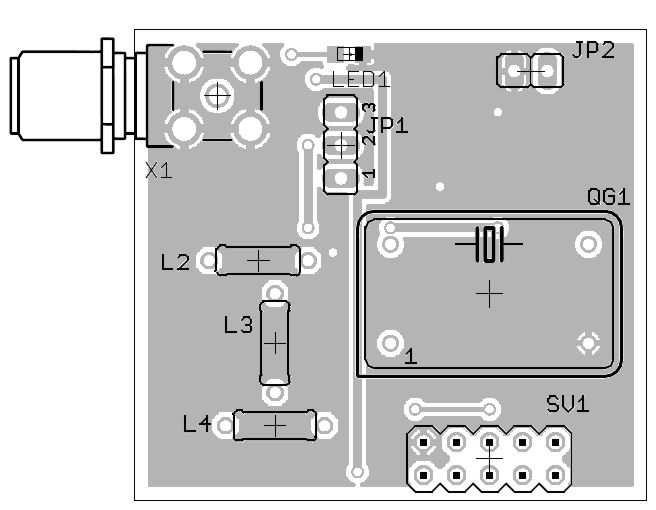

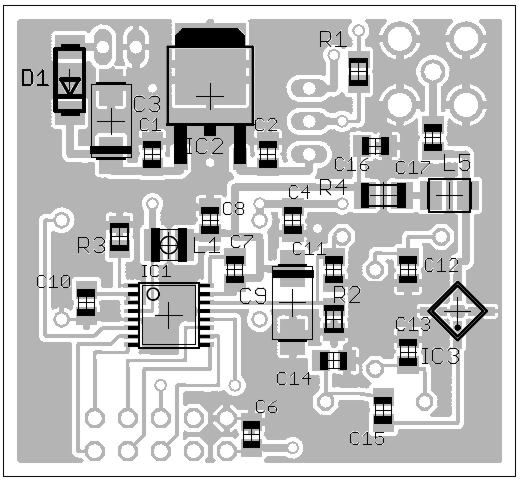

Obvod AD9832 je ve schématu zapojení na předchozím obrázku zapojen v katalogovém zapojení s tím, že je ponechána možnost měnit registr frekvence jak fyzicky, přivedením log 1 na příslušný pin,

tak i softwarově v rámci inicializace obvodu. Stejně tak je řešeno i použití fázových registrů. Ty lze přepínat také buď pomocí příslušných pinů nebo běheme inicializace softwarově.

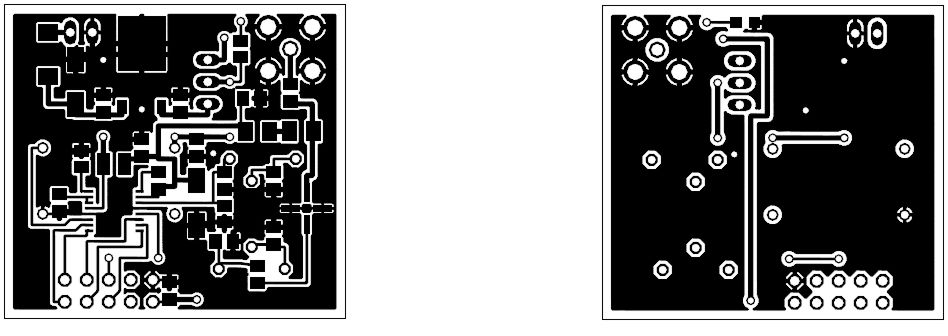

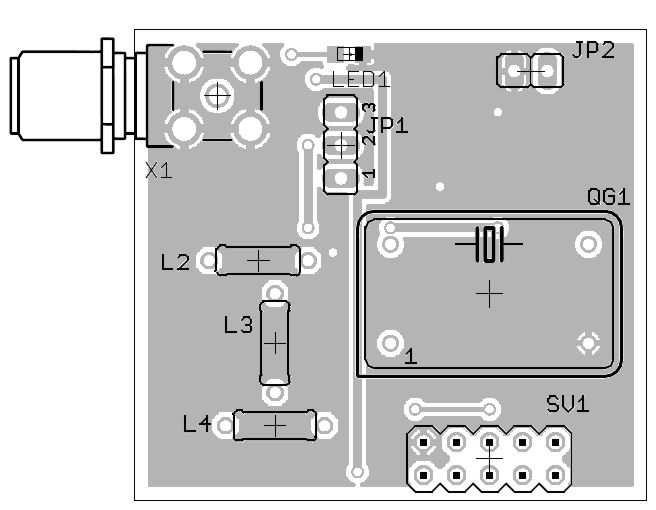

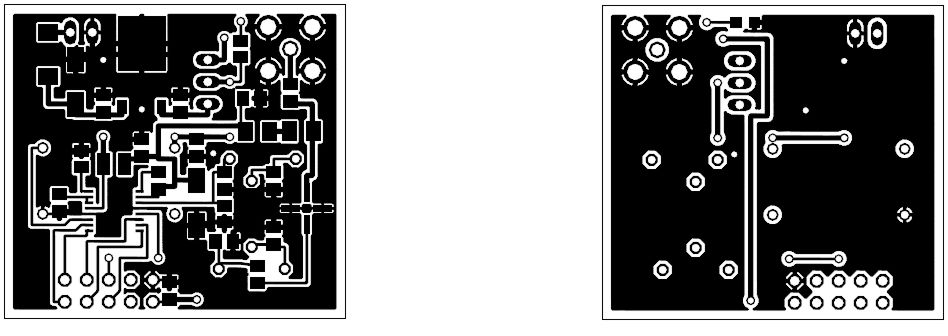

Na výstupu DDS je zapojen filtr typu DP s trojicí π článků a mezním kmitočtem fm = 12 MHz. Na výstupu filtru je zařazen širokopásmový zesilovač MMIC typu MAR-1 z produkce firmy Minicircuits [3],

který zaručuje zesílení minimálně 18 dB v celém uvažovaném pásmu kmitočtů. Výstupní impedance obvodu je standardních 50 Ω. Celý testovací generátor je osazen na oboustranné desce plošných spojů o ozměrech 39 x 39 mm.

Obvod AD9832 je ve schématu zapojení na předchozím obrázku zapojen v katalogovém zapojení s tím, že je ponechána možnost měnit registr frekvence jak fyzicky, přivedením log 1 na příslušný pin,

tak i softwarově v rámci inicializace obvodu. Stejně tak je řešeno i použití fázových registrů. Ty lze přepínat také buď pomocí příslušných pinů nebo běheme inicializace softwarově.

Na výstupu DDS je zapojen filtr typu DP s trojicí π článků a mezním kmitočtem fm = 12 MHz. Na výstupu filtru je zařazen širokopásmový zesilovač MMIC typu MAR-1 z produkce firmy Minicircuits [3],

který zaručuje zesílení minimálně 18 dB v celém uvažovaném pásmu kmitočtů. Výstupní impedance obvodu je standardních 50 Ω. Celý testovací generátor je osazen na oboustranné desce plošných spojů o ozměrech 39 x 39 mm.

Komunikace obvodu AD9832 s řídicím mikroprocesorem probíhá po sběrnici SPI, doplněnou o jednoduchou signalizaci. Ovládaný obvod je v režimu SLAVE a využívá následující vývody:

SDATA - > MOSI

SCLK - > SCK

FSYNC - > signalizace rámce např. PB0

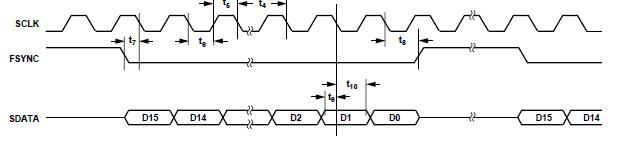

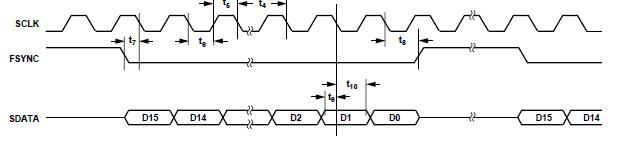

Na následujícím obrázku se nachází časovací diagram komunikace. Nejdůležitějším údajem je maximální použitelný kmitočet hodinového signálu SCK, který je stejně jako maximální kmitočet hodinového signálu MCLK

fmax = 25MHz. Z obrázku je patrné, jak fyzická komunikace probíhá. Nejprve je uveden signál FSYNC do log 0, s jehož sestupnou hranou je zahájeno vysílání rámce dat o délce 16 bitů. Tato

data jsou vysíláno od MSB po LSB. Jakmile je odeslán bit LSB, je komunikace ukončena nastavením FSYNC do log 1.

Komunikace obvodu AD9832 s řídicím mikroprocesorem probíhá po sběrnici SPI, doplněnou o jednoduchou signalizaci. Ovládaný obvod je v režimu SLAVE a využívá následující vývody:

SDATA - > MOSI

SCLK - > SCK

FSYNC - > signalizace rámce např. PB0

Na následujícím obrázku se nachází časovací diagram komunikace. Nejdůležitějším údajem je maximální použitelný kmitočet hodinového signálu SCK, který je stejně jako maximální kmitočet hodinového signálu MCLK

fmax = 25MHz. Z obrázku je patrné, jak fyzická komunikace probíhá. Nejprve je uveden signál FSYNC do log 0, s jehož sestupnou hranou je zahájeno vysílání rámce dat o délce 16 bitů. Tato

data jsou vysíláno od MSB po LSB. Jakmile je odeslán bit LSB, je komunikace ukončena nastavením FSYNC do log 1.

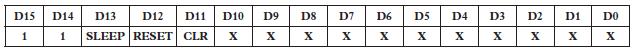

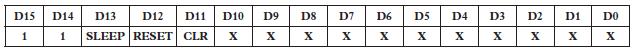

Komunikace s obvodem začíná odesláním jednoho 16 bitového rámce, kde je provedeno probuzení obvodu z režimu "power down" a jeho reset:

Komunikace s obvodem začíná odesláním jednoho 16 bitového rámce, kde je provedeno probuzení obvodu z režimu "power down" a jeho reset:

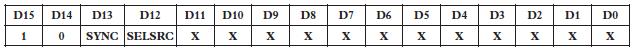

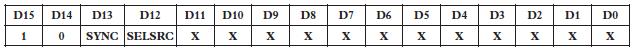

Následuje výběr ovládání fázových a frekvenčních registrů pomocí příznaku SELSRC v následujícím rámci. Jakmile je SELSRC = 1, jsou použity pro přepínání registrů přímo konkrétní

piny obvodu AD9832. V tomto rámci je také možnost nastavit synchronizaci dat s hodinami MCLK a to, pokud je příznak SYNC = 1, jinak není synchronizace použita.

Následuje výběr ovládání fázových a frekvenčních registrů pomocí příznaku SELSRC v následujícím rámci. Jakmile je SELSRC = 1, jsou použity pro přepínání registrů přímo konkrétní

piny obvodu AD9832. V tomto rámci je také možnost nastavit synchronizaci dat s hodinami MCLK a to, pokud je příznak SYNC = 1, jinak není synchronizace použita.

Dále je třeba zvolit konkrétní frekvenční registry (FREG0 nebo FREG1) a fázové registry (PHASEREG 0 - 3) a ty naplnit daty. Registry FREG0 a 1 jsou 32 bitové narozdíl od 12 bitových

fázových registrů PHASEREG 0 - 3. Tomu musí pochopitelně odpovídat odesílaná data. Zatímco obsah registru frekvence nám přímo určuje frekvenci výstupního signálu, tak registry fáze nemusíme

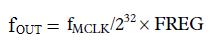

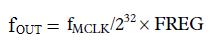

vůbec použít. Ty umožňují vytvoření definovaného fázového posuvu signálu, čehož lze snadno vyzžít například k vytvoření modulace QPSK (máme 4 fázové registry). Výstupní frekvence DDS je dána vztahem,

kde: FREG je 32 bitový obsah zvoleného registru FREG0 nebo 1 a fmclk je kmitočet hodinového signálu. Vztah pro výstupní kmitočet:

Dále je třeba zvolit konkrétní frekvenční registry (FREG0 nebo FREG1) a fázové registry (PHASEREG 0 - 3) a ty naplnit daty. Registry FREG0 a 1 jsou 32 bitové narozdíl od 12 bitových

fázových registrů PHASEREG 0 - 3. Tomu musí pochopitelně odpovídat odesílaná data. Zatímco obsah registru frekvence nám přímo určuje frekvenci výstupního signálu, tak registry fáze nemusíme

vůbec použít. Ty umožňují vytvoření definovaného fázového posuvu signálu, čehož lze snadno vyzžít například k vytvoření modulace QPSK (máme 4 fázové registry). Výstupní frekvence DDS je dána vztahem,

kde: FREG je 32 bitový obsah zvoleného registru FREG0 nebo 1 a fmclk je kmitočet hodinového signálu. Vztah pro výstupní kmitočet:

Naplnění registrů FREG proběhne vzápětí po volbě aktivního registru, případně odeslání dalších dodatečných nastavení, které jsou popsány v katalogovém listu obvodu [1].

Naplnění registrů FREG proběhne vzápětí po volbě aktivního registru, případně odeslání dalších dodatečných nastavení, které jsou popsány v katalogovém listu obvodu [1].

Knihovna je určena pro použití s mikroprocesorem ATMEL ATmega16 [4].

Vzhledem k poškození vývojové desky je tato knihovna nedokončená a obsahuje pouze funkce pro inicializaci SPI rozhraní mikroprocesoru a funkci pro odeslání 16 bitového bloku dat. Dále je nutné doplnit funkce pro

inicializaci obvodu AD9832, odeslání (změnu) výstupního kmitočtu s možností změny registru FREG. Dále bude vhodné napsat funkce pro uspání, reset a probuzení obvodu, stejně jako funci, umožňující

fázovou modulaci.

Funkce obsažené v knihovně:

void SPI_init (void);

void SPI_write16 (unsigned short data);

V rámci tohoto projektu se mi podařilo navrhnout a zkonstruovat jednoduchý testovací přípravek s obvodem AD9832, který je schopen generovat sinusový kmitočet o frekvenci 0 - 6 MHz. Jednotlivé

bloky obvodu nevykazují známky nefunkčnosti. Obvod byl navržen pro co možná nejuniversálnější použití se všemi možnostmi ovládání, které daný obvod poskytuje. Takto zapojený modul nalezne využití

například i ve školních laboratořích.

Bohužel se mi však z důvodu špatného časového rozvržení práce a následně z důvodu poškození vlastní vývojové desky pro ATmega16, nepodařilo dokončit knihovnu pro ovládání obvodu a tudíž ani ukázkový

program. Vzhledem k faktu, že tento modul hodlám nadále vyvýjet a využívat v několika jiných projektech, bude knihovna dokončena v nejkratším možném termínu.

Odkaz pro stažení projektu:

projektu.

[1] AD8302, Data sheet [online]. Analog Devices, 2002 – [cit. 24 května 2009]. Dostupné na: www.analog.com

[2] Dresler, Tomáš. Přímá číslicová syntéza kmitočtu (DDS - Direct Digital Synthesis), Odborný článek [online]. 2001 – [cit. 24. května 2009]. Dostupné na: Direct-Digital-Synthesis

[3] Mini-Circuits, Oficiální stránky firmy Mini-Circuits [online]. 2009 – [cit. 24. května 2009]. Dostupné na: www.minicircuits.com

[4] Atmel, Oficiální stránky firmy Atmel [online]. 2007 – [cit. 24. května 2009]. Dostupné na: www.atmel.com

feec.vutbr.cz

feec.vutbr.cz

feec.vutbr.cz

feec.vutbr.cz